# (19)日本国特許庁(JP)

# (12) 公開特許公報(A)

(11)特許出願公開番号

# 特開平10-284589

(43)公開日 平成10年(1998)10月23日

| (51) Int.Cl. <sup>6</sup> |       | 識別記号 | FΙ   |       |      |

|---------------------------|-------|------|------|-------|------|

| H01L                      | 21/76 |      | H01L | 21/76 | L    |

|                           | 29/78 |      |      | 29/78 | 301R |

|          |                | 審査請求 有 請求項の数11 OL (全 10 頁)                      |

|----------|----------------|-------------------------------------------------|

| (21)出願番号 | 特願平9-85082     | (71)出願人 000004237<br>日本電気株式会社                   |

| (22)出顧日  | 平成9年(1997)4月3日 | 東京都港区芝五丁目7番1号 (72)発明者 西川 一志 東京都港区芝五丁目7番1号 日本電気株 |

|          |                | 式会社内<br>(74)代理人 弁理士 若林 忠                        |

|          |                |                                                 |

#### (54) 【発明の名称】 半導体装置及びその製造方法

# (57)【要約】

【課題】トレンチ(溝)によって素子分離されたMOS トランジスタを有する半導体装置において、素子を微細 化した場合であっても、MOSトランジスタのサブスレ ッショルド特性を劣化させることなく、素子分離特性を 向上させる。

【解決手段】p型シリコン基板1の全面にボロンイオン 3のイオン注入を行うことにより、基板表面から一定の 深さのところに、チャネルストッパとなる p - 層 4 を形 成する。その後、トレンチ分離のための溝部7をその底 面がp-層4に達するように形成し、溝部7で囲まれた 素子形成領域内にMOSトランジスタを形成する。

( ~

## 【特許請求の範囲】

【請求項1】 半導体基板の表面から所定の深さの位置に帯状に形成された前記半導体基板と同一導電型で前記半導体基板より高濃度の不純物層と、前記半導体基板の表面から前記不純物層に向けて、少なくとも一部が前記不純物層まで届くように形成された分離溝とを有することを特徴とする半導体装置。

【請求項2】 前記不純物層が前記同一導電型の不純物のイオン注入によって形成された層である請求項1に記載の半導体装置。

【請求項3】 前記不純物層が、前記一定の深さの位置 に濃度ピークを有するように一様に形成されている請求 項1または2に記載の半導体装置。

【請求項4】 不純物濃度が、前記分離溝と前記半導体 基板との界面に反転層を生じさせない濃度である、請求 項1に記載の半導体装置。

【請求項5】 前記不純物層の一定の深さが、前記分離 溝で囲まれた半導体基板上に形成された少なくとも1つ のMOSトランジスタのサブスレッショルド特性が劣化 することがない深さである、請求項1乃至4いずれか1 項に記載の半導体装置。

【請求項6】 半導体基板の一主面側から前記半導体基板の内部に前記半導体基板と同一導電型の不純物をイオン注入する工程と、前記イオン注入の後に、前記主面側から素子形成領域を囲むように前記半導体基板に溝を形成する工程とを有し、

前記溝の深さは、前記イオン注入によって形成された不 純物層において前記不純物の濃度が所定の濃度となる深 さ以上の深さであることを特徴とする半導体装置の製造 方法。

【請求項7】 所定の導電型の半導体基板上に少なくと も1つのMOSトランジスタを有する半導体装置の製造 方法において、

前記半導体基板の一主面に第1の絶縁膜を形成する工程と、前記第1の絶縁膜を介して前記半導体基板の内部に前記所定の導電型の不純物をイオン注入する工程と、前記イオン注入の後に、前記主面側から素子形成領域を囲むように前記半導体基板に溝を形成する工程と、前記イオン注入された不純物を活性化するために熱処理を行う工程と、前記溝の露出面に第2の絶縁膜を形成する工程 40と、前記素子形成領域にMOSトランジスタを形成する工程とを有し、

前記溝の深さは、前記イオン注入によって形成された不 純物層において前記不純物の濃度が所定の濃度となる深 さ以上の深さであることを特徴とする半導体装置の製造 方法。

【請求項8】 前記第1の絶縁膜を選択的に除去してから異方性エッチングを行うことにより前記溝が形成される請求項6または7に記載の半導体装置の製造方法。

【請求項9】 前記第2の絶縁膜の形成後、前記溝の内

部及び前記主面上に多結晶シリコン層を形成する工程と、前記多結晶シリコン層をエッチバックして前記溝の内部のみに多結晶シリコンを残存させる工程とを有し、前記エッチバックを行った後に前記MOSトランジスタを形成する請求項6または7に記載の半導体装置の製造方法。

【請求項10】 深さ方向の不純物分布によって前記MOSトランジスタのサブスレッショルド特性が劣化することがないように、前記所定の導電型の不純物をイオン注入する際の注入エネルギーを制御する、請求項6または7に記載の半導体装置の製造方法。

【請求項11】 前記所定の濃度が、前記溝と前記半導体基板との界面に反転層を生じさせない濃度である、請求項6または7に記載の半導体装置の製造方法。

### 【発明の詳細な説明】

[0001]

【発明の属する技術分野】本発明は、半導体基板上にMOS(Metal-Oxide-Semiconductor)電界効果トランジスタを有する半導体装置に関し、特に、素子サイズを微細化した際にトランジスタのサブスレッショルド特性が劣化しない半導体装置及びその製造方法に関する。

#### [0002]

【従来の技術】半導体基板上にMOSトランジスタを有 する半導体装置では、従来、選択酸化膜「LOCOS(L ocal Oxidation of Silicon)膜]を形成して素子分離を 行っていた。その際、半導体基板のLOCOS膜の下面 に接する部位には、その半導体基板の導電型と同じ導電 型の不純物を基板での不純物濃度よりも濃く注入してチ ャネルストッパ領域を形成し、寄生チャネルによる影響 がMOSトランジスタなどに及ばないようにしている。 30 近年、半導体装置における素子の微細化が積極的に進め られているが、LOCOS膜による素子分離では素子間 の間隔をそれほど狭くすることができず、また、チャネ ルストッパを深い位置に形成できないため、LOCOS 膜形成以外の方法による素子分離の方法が実施されるよ うになってきた。例えば、特開平4-354148号公 報には、半導体基板の全面に酸化膜を形成した後、素子 分離領域となる部分の半導体基板に酸化膜を介してチャ ネルストッパ用の不純物をイオン注入し、その後、素子 形成領域の酸化膜を除去する技術が開示されている。し かしながら、この技術では、チャネルストッパ領域を深 い位置に形成できないので、サイドウォールを形成する 必要があり、また、パンチスルーが起こる可能性があ る.

【0003】また、トレンチ(溝)を形成して素子分離を行う技術も知られている。トレンチで素子分離を行う場合、トレンチを十分に深く形成することができるのであれば、トレンチだけで十分な素子分離特性を得ることができる。しかしながら、トレンチを深く形成すること 50 は、製造プロセスのスループットを低下させるなど好ま

3

しくない。そこで、トレンチを比較的浅く形成することが考えられるが、トレンチを比較的浅く形成した場合には、寄生チャネルによる影響を防ぐため、LOCOS膜で素子分離する場合と同様に、トレンチの底部にチャネルストッパ領域を形成する必要がある。

【0004】例えば、特開昭57-23240号公報に は、高性能であって集積度の高い半導体装置を製造する ことを目的として、半導体基板の所望の部分に溝(トレ ンチ)を形成し、溝内が絶縁膜で充填されるように基板 上に絶縁膜を堆積させ、その後、溝内部のみに絶縁膜が 残存するようにこの絶縁膜をエッチバックし、フィール ド領域を形成することが開示されている。この公報で は、絶縁膜を堆積する前に、溝の部分のみに選択的に、 基板と同じ導電型の不純物をイオン注入し、溝の底部に チャネルストッパ領域を形成することが示されている。 また、特開平2-119137号公報には、表面が平坦 であってバーズビーグがない素子分離用酸化膜を形成で きる方法を提供することを目的として、半導体基板の表 面に所定の深さの溝を形成して素子形成領域を画定し、 溝の底部に選択的にイオン注入を行ってチャネルストッ パ領域を形成し、その後、溝部のみを選択酸化して溝を 酸化シリコンで埋め戻し、素子分離用酸化膜とすること が開示されている。

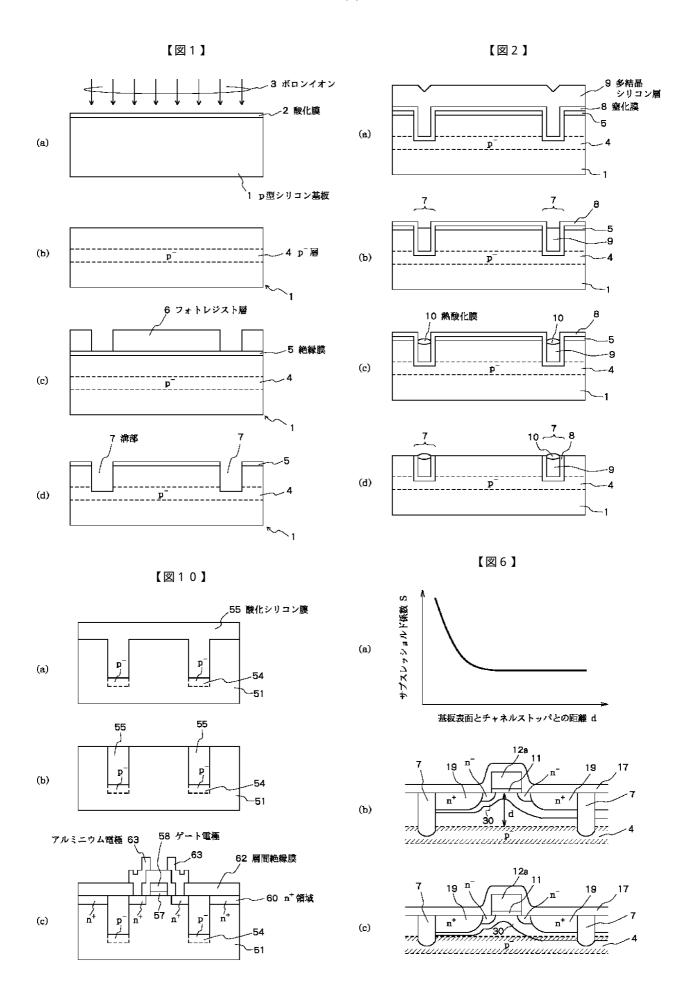

【0005】図9(a)~(c)及び図10(a)~(c)は、このように半導体基板にトレンチを形成するとともに、トレンチの底部にチャネルストッパ領域を形成して半導体装置を製造する従来の方法での各工程を順を追って説明する断面図である。ここでは、nチャネルMOSトランジスタを製造するものとする。

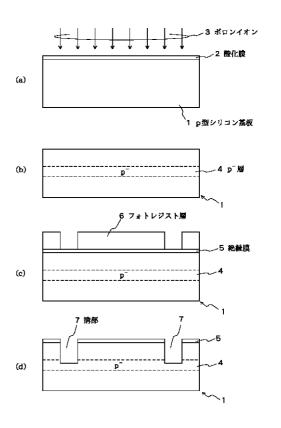

【0006】まず、図9(a)に示すように、p型シリコン基板51上に、溝を形成すべき部分のみが開口したレジストパターン52を設け、図9(b)に示すように、レジストパターン52をマスクとしたイオンエッチングにより、p型シリコン基板51に溝部53を形成する。溝部53を形成したら、レジストパターン52をマスクとしてボロンのイオン注入を行い、図9(c)に示すように、溝部53の底部にあたる領域のp型シリコン基板51内に、チャネルストッパ領域となるp-領域54を形成する。このp-領域54は、底面として溝部53内で露出している。

【0007】次に、レジストパターン52を除去し、図10(a)に示すように、溝部53内が酸化シリコンで充填されるように、CVD(化学的気相成長)法により、p型シリコン基板51の全面に酸化シリコン膜55を成膜する。そして、図10(b)に示すように、溝部53以外の領域でp型シリコン基板51の表面が露出するように酸化シリコン膜55をエッチバックする。このとき、溝部53の内部は酸化シリコン膜55が充填された状態のままであり、p型シリコン基板51の表面は平坦となっている。その後、ゲート酸化膜57及びゲート電極5

4

8を形成し、イオン注入によってドレイン領域及びソース領域となる n+領域 6 0 を形成し、層間絶縁膜 6 2 を設け、ドレイン電極及びソース電極となるアルミニウム (A1)電極 6 3 を設けて、図 1 0 (c)に示すように半導体装置が完成する。

# [0008]

【発明が解決しようとする課題】しかしながら、上述し た従来の半導体装置では、微細化を進めて分離溝(トレ ンチ)が細くなった場合、基板と同じ導電型の不純物を 分離溝の底面にイオン注入しようとしても、注入濃度を 高めることができずに所望のチャネルストッパ領域が形 成されないという問題点がある。さらに、分離溝が細い 場合には、イオン注入での工程上の問題から、溝の底面 のみのイオン注入を行うことが難しく、どうしても、溝 の側壁にも、基板と同導電型の不純物が注入されてしま うことになる。溝の側壁でのこのように不純物が注入さ れた領域は、チャネルストッパ領域と同様に作用し、こ の領域とMOSトランジスタのソース領域やドレイン領 域が接近しているため、サブスレッショルド特性の悪化 をもたらす。さらに、溝形状の部分へのイオン注入は、 シミュレーションなどによる評価が難しいという問題点 もある。

【0009】本発明の目的は、微細化を推し進めた場合であっても、寄生チャネルの影響なく素子分離を十分に行え、かつ、サブスレッショルド特性も悪化しない半導体装置とその製造方法を提供することにある。

### [0010]

【課題を解決するための手段】本発明の半導体装置は、 半導体基板の表面から所定の深さの位置に帯状に形成された前記半導体基板と同一導電型で前記半導体基板より 高濃度の不純物層と、前記半導体基板の表面から前記不 純物層に向けて、少なくとも一部が前記不純物層まで届 くように形成された分離溝とを有する。

【0011】本発明の半導体装置においては、不純物層はイオン注入によって形成することが好ましい。また、不純物層は、少なくとも分離溝で囲まれた領域(素子形成領域)において、一定の深さの位置に濃度ピークを有するように一様に形成されていることが好ましい。一定の深さの深さとは、典型的には、導入された不純物によりMOSトランジスタのサブスレッショルド特性が劣化することがない深さであり、所定の不純物濃度とは、不純物層がチャネルストッパとして機能するような濃度、典型的には、溝と半導体基板との界面に反転層を生じさせない濃度である。

【 0 0 1 2 】本発明の半導体装置の製造方法は、半導体基板の一主面側から前記半導体基板の内部に前記半導体基板と同一導電型の不純物をイオン注入する工程と、前記イオン注入の後に、前記主面側から素子形成領域を囲むように前記半導体基板に溝を形成する工程とを有し、前記溝の深さは、前記イオン注入によって形成された不

50

純物層において前記不純物の濃度が所定の濃度となる深 さ以上の深さである。

【0013】本発明の半導体装置の製造方法において は、半導体基板の一主面に第1の絶縁膜を形成する工程 と、イオン注入された不純物を活性化するために熱処理 を行う工程と、溝の露出面に第2の絶縁膜を形成する工 程とを備え、第1の絶縁膜を介してイオン注入が行われ るようにすることが好ましい。その場合、溝は、第1の 絶縁膜を選択的に除去してから異方性エッチングを行う ことにより形成できる。さらに、第2の絶縁膜の形成 後、溝の内部及び主面上に多結晶シリコン層を形成する 工程と、多結晶シリコン層をエッチバックして溝の内部 のみに多結晶シリコンを残存させる工程とを設け、エッ チバックを行った後にMOSトランジスタを形成するこ とが好ましい。イオン注入時の注入エネルギーは、深さ 方向の不純物分布によってMOSトランジスタのサブス レッショルド特性が劣化することがないように制御する ことが好ましい。また、所定の濃度は、イオン注入によ って形成される層がチャネルストッパとして機能するよ うな濃度であり、具体的には、溝と半導体基板との界面 に反転層を生じさせない濃度とすることが好ましい。

【0014】本発明では、シリコン基板などの半導体基板の内部の一定の深さのところにイオン注入などによりチャネルストッパ領域となる層を予め形成し、その後、素子分離領域を構成する溝(トレンチ)を形成する。その結果、チャネルストッパ領域の形成時には溝が存在していないので、チャネルストッパでの不純物濃度を十分に高めることができる。また、溝の側壁へのイオン注入に伴うサブスレッショルド特性の悪化が起こらず、イオン注入のシミュレーションも簡単に行うことができるようになる。

【0015】本発明の構成の場合、MOSトランジスタのチャネル領域の下方にもチャネルストッパが存在することになるが、イオン注入のエネルギーなどを制御することにより、チャネル領域とチャネルストッパとを十分に離すことが可能であり、したがって、サブスレッショルド特性が悪化することを十分に予防できる。

# [0016]

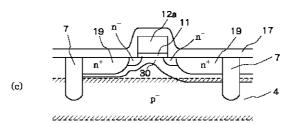

【発明の実施の形態】次に、本発明の実施の好ましい形態について、図面を参照して説明する。ここでは、p型シリコン基板に、トレンチによって素子分離されたnチャネルMOSトランジスタを形成する場合について説明する。図1(a)~(d)、図2(a)~(d)、図3(a)~(d)及び図4(a)~(c)は、本発明の実施の一形態の半導体装置の製造方法を順を追って説明する断面図である。

【0017】本実施の形態の半導体装置は、p型シリコン基板の一方の主面(以下、単に表面という)にLDD(Lightly Doped Drain)構造のnチャネルMOSトランジスタが形成された構造のものであり、このnチャネルMOSトランジスタを囲むように素子分離領域が設けら

6

れ、素子分離領域には溝部(トレンチ)が形成され、こ の溝部によってMOSトランジスタの素子分離が行われ ている。「従来の技術」の欄でも述べたように、溝部の 底部に接するようにチャネルストッパ領域を設ける必要 があるが、本実施の形態の半導体装置では、溝部の底部 だけでなく、MOSトランジスタのチャネル領域の下方 にあたる位置にもチャネルストッパ領域が設けられてい る。具体的には、p型シリコン基板の内部であって、p 型シリコン基板の表面から一定の深さのところに、一様 10 に、チャネルストッパ領域となるべき p · 層が形成され ている。この p · 層は、溝部を形成する前に基板に対し てイオン注入を行うことによって形成される。溝部の底 面はp<sup>-</sup>層にまで達しており、これにより、p<sup>-</sup>層が、素 子分離用の溝部に対するチャネルストッパ領域として作 用することになる。なお、この半導体装置においては、 MOSトランジスタのチャネル領域の下方にもチャネル ストッパ領域が存在することから、サブスレッショルド 特性を悪化させないように、チャネルストッパ領域の深 さやチャネルストッパ領域における不純物の深さ方向の 分布を適切に制御する必要がある。この深さや不純物分 布については後述する。

【0018】この半導体装置の製造工程について、詳細に説明する。

【0019】まず、図1(a)に示すように、表面に薄い酸化膜2が形成されたp型シリコン基板1に対し、その酸化膜2を介してボロン(B)イオン3を全面にイオン注入し、p型シリコン基板1の表面からほぼ一定の深さのところに、チャネルストッパ領域となるp・層4を形成する。このとき、ボロンイオン3の注入エネルギーを制御して、このp・層4の形成深さを制御し、できあがるMOSトランジスタのサブスレッショルド特性を制御するようにする。詳細については後述する。その後、酸化膜2を除去する。図1(b)は、イオン注入が終了し酸化膜2が除去された状態を示している。

【0020】次に、p型シリコン基板1の表面の全面に酸化シリコンなどで構成した薄い絶縁膜5を形成し、絶縁膜5上にフォトレジスト層6を設け、フォトリゾグラフィ技術を用いて、素子分離領域となる部分(トレンチを形成する部分)だけ、図1(c)に示すようにフォトレジストを除去する。なお、本実施の形態では、図1(b)にしめすようにp型シリコン基板1の表面の酸化膜2を除去してから、図1(c)に示すように絶縁膜5をp型シリコン基板1の表面に改めて形成しているが、酸化膜2を除去せずに、この酸化膜2をそのまま絶縁膜5として用いてもよい。

【 0 0 2 1】次に、フォトレジスト層 6 をマスクとして 絶縁膜 5 をエッチングすることにより、素子分離領域と なる部分のみ、絶縁膜 5 を除去する。そして、残存して いるフォトレジストを全て除去し、上述したようにパタ 50 ーニングされている絶縁膜 5 をマスクとして、例えば、

30

7

異方性イオンエッチングなどにより p型シリコン基板 1 をエッチングし、図1(d)に示すように、素子分離領域 となる部分に溝部7を形成する。溝部7は、素子形成領 域(MOSトランジスタが形成される領域)を囲むよう に、例えば、口の字型の平面形状で設けられる。エッチ ングの条件は、溝部7の底面の位置が少なくともp-層 4に達するように、具体的には、ボロン濃度が所定の濃 度となる深さよりも深い位置に達するように、設定され る。この所定の濃度は、チャネルストッパとして有効に 作用するようなボロン濃度として定められる。 溝部 7 を 形成したら、 p型シリコン基板 1上の絶縁膜 5上、及び 溝部7の底面及び側面に、窒化シリコンからなる窒化膜 8を例えば CVD法によって堆積する。この窒化膜 8 は、トレンチ分離での素子分離用絶縁物となるものであ るから、特に溝部7の内部において、ピンホールなどが 生じないように形成する。さらに、窒化膜8上に、溝部 7を充填するとともにp型シリコン基板1の表面全体を 覆うように、比較的厚い多結晶シリコン (ポリシリコ ン)層9を形成する。多結晶シリコン層9が形成された 状態を図2(a)に示す。

【0022】次に、溝部7以外では窒化膜8が露出するように、多結晶シリコン層9をエッチバックする。溝部7の内部では、多結晶シリコンが残存するようにする。具体的には、図2(b)に示すように、溝部7では、窒化膜8の下の絶縁膜5の断面位置とほぼ同じレベルの位置に多結晶シリコンの表面が位置するようにする。次に、熱酸化法により、図2(c)に示すように、溝部7内部の多結晶シリコンの表面に熱酸化膜10を形成する。そして、図2(d)に示すように、窒化膜8をエッチングして溝部7以外の部分にある窒化膜8を除去し、さらに、絶30縁膜5を除去し、溝部7以外でp型シリコン基板1の表面を露出させる。

【0023】続いて、このように露出させた表面の全面にゲート酸化膜11を形成し、このゲート酸化膜11上に、多結晶シリコン層12を形成する。多結晶シリコン層12の上には、ゲート電極を形成すべき位置にのみ、フォトリソグラフィ法によってフォトレジスト層13を形成する。この状態を図3(a)に示す。このフォトレジスト層13をマスクとして多結晶シリコン層12のエッチングを行い、ゲート電極12aを形成する。

【0024】ゲート電極12 aが形成されたら、今度は、このゲート電極12をマスクとして、LDD領域形成のために、図3(b)に示すように、リン(P)イオン14をイオン注入し、ゲート電極12の下の部分を除いて、p型シリコン基板1の最表面にn<sup>-</sup>層15を形成する。リンのイオン注入の後、図3(c)に示すように表面の全面に酸化膜16を形成し、この酸化膜16をエッチバックすることにより、図3(d)に示すように、ゲート電極12aの側面部分に、サイドウォール16aを形成する。

8

【0025】次に、全面に比較的薄い酸化膜17を形成 し、図4(a)に示すように、この酸化膜17を介し、ゲ ート電極12aとサイドウォール16aをマスクとし て、ヒ素(As)イオン18をp型シリコン基板1にイオ ン注入し、ドレイン領域及びソース領域を構成する n+ 層19を形成する。その後、図4(b)に示すように、酸 化膜17上の全面に層間絶縁膜20を形成し、さらに、 層間絶縁膜20上にフォトレジスト層21を設け、電極 形成位置のフォトレジストを除去されるようにフォトレ ジスト層 2 1 のパターニングを行う。最後に、図 4 (c) に示すように、パターニングされたフォトレジスト層2 1をマスクとして層間絶縁膜20及び酸化膜17のエッ チングを行ってドレイン電極及びソース電極用の開口を 設け、アルミニウムあるいは多結晶シリコンなどからな る電極22を設ける。電極22は、ソース領域、ドレイ ン領域のぞれぞれに設けられ、対応するn+層19とオ ーミック接合を形成している。

【0026】以上のようにして、本実施の形態の半導体 装置が完成する。なお、上述の工程においては、例えば 熱酸化によって絶縁膜5を形成するものとすると、この 際の熱処理によって、p-層4として導入されたボロン の活性化や拡散も行われる。 具体的には、溝部7の底面 の位置でのボロン濃度が、溝部7とp型シリコン基板1 との界面に反転層が生じないようなボロン濃度になるよ うな拡散条件での熱処理が行われるようにする。絶縁膜 5を形成する際に熱酸化を用いないものとしても、熱酸 化膜10の形成の際の熱処理によって、ボロンの活性化 や拡散が行われる。以上の説明では、n-層15やn+層 19の活性化については特に触れていないが、当然のこ とながら、これら層の活性化の工程も実施されている。 【 0 0 2 7 】次に、チャネルストッパ領域となる p · 層 4について説明する。本実施の形態半導体装置では、p 型シリコン基板1の全面に対し、ある一定の深さのとこ ろに不純物濃度のピークが位置するようにボロンイオン を打ち込み、p<sup>-</sup>層4としている。イオン注入を用いて いるので、ピーク深さ (イオン注入したボロンの濃度が 最大となる深さ)を中心にして深さ方向にある広がりを もって分布する。ここでイオン注入するボロン量を増や し、ピーク深さでのボロン濃度を高めると、不純物分布 の裾にあたる部分での濃度も増加する。この半導体装置 では、MOSトランジスタのチャネル領域の真下の位置 にもp 層 4 が存在するため、ピーク深さでのボロン濃 度を高くしすぎると、チャネル領域近傍でのボロン濃度 も高くなり、結果としてMOSトランジスタのサブスレ ッショルド係数が大きくなって、サブスレッショルド特 性が悪化する。

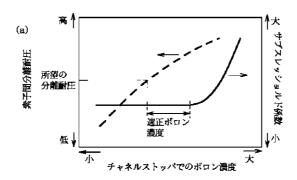

【0028】図5(a)は、以上のような観点からボロン 濃度の最適値を説明する図である。チャネルストッパの ボロン濃度(例えばピーク深さでのボロン濃度)と、素 50 子間分離耐圧及びサブスレッショルド係数との関係を模

式的に示している。ここではピーク深さは一定であるとしている。ボロン濃度を高めるほど素子間分離耐圧は高まる。一方、サブスレッショルド係数は、ボロン濃度がある値以下ではほぼ一定であるが、ボロン濃度がこの値を上回ると、急速に大きくなる。したがって、本実施の形態では、所望の分離耐圧が得られるボロン濃度以上であって、サブスレッショルド係数が立ち上がるボロン濃度以下のボロン濃度がイオン注入での適正なボロン濃度となる。

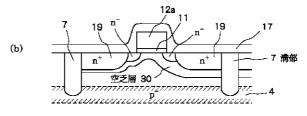

【0029】図5(b)は、ボロン濃度が適正であるとき の、MOSトランジスタの動作に伴う空乏層30とp-層4との関係を示す図である。ハッチング(斜線)が付 された破線ではさまれた領域は、サブスレッショルド特 性を劣化させてしまうようなボロン濃度(例えば図5 (a)でサブスレッショルド係数が立ち上がる点のボロン 濃度)の領域である。図5(b)の場合では、サブスレッ ショルド特性を劣化させてしまうようなボロン濃度の領 域が空乏層30から十分に離れているため、MOSトラ ンジスタのサブスレッショルド特性が劣化することがな い。なお、溝部7の底面は、サブスレッショルド特性が 劣化するようなボロン濃度の領域であって、所望の素子 間分離耐圧を実現できるようなボロン濃度の位置(この ようなボロン濃度の位置は不純物分布の両側に考えられ るが、ここでは、p型シリコン基板1の表面に近い側の 位置)か、それよりも深い位置に達している。ここで溝 部7の底面の位置とは、p型シリコン基板1をエッチン グしてその溝部7を形成する際に、p型シリコン基板1 のエッチング表面のうちエッチングされていない表面か らの距離が最大(最深)である点の位置のことである。 【0030】図5(c)は、ボロン濃度が高すぎる場合に おける空乏層30とp-層4との関係を示す図である。 ボロン濃度が高すぎるため、サブスレッショルド特性を 劣化させるようなボロン濃度の領域が p 型シリコン基板 1の表面近くまで広がっており、この領域内に空乏層3 0の一部がかかっている。その結果、MOSトランジス タのサブスレッショルド特性が劣化する。

【0031】次に、p・層4の深さについて検討する。図6(a)は、基板表面からチャネルストッパ領域であるp・層4までの距離 d と、サブスレッショルド係数5と関係を示すグラフである。ここでは、ボロンのドーズ量は一定であり、注入エネルギーを変えることによってピーク深さを制御し、距離 d を変化させているものとする。距離 d が小さいほどサブスレッショルド係数5 は大きくなり、サブスレッショルド特性が悪化するが、距離 d がある値より大きい場合には、サブスレッショルド係数はほぼ一定となっている。ここで距離 d は、図6(b)に示すように、p型シリコン基板1の表面からイオン注入されたボロンの濃度がある所定の値以上の領域(図示、ハッチングが付された破線ではさまれた領域)まで距離とする。図6(c)はイオンの注入エネルギーが小さ

10

くて距離 d が小さすぎる場合の空乏層 3 0 と p · 層 4 と の関係を示している。この場合は、チャネルストッパが 浅いので溝部 7 も浅く形成することができるが、空乏層 3 0 が形成される領域でのボロン濃度が高く、サブスレッショルド特性が劣化する。

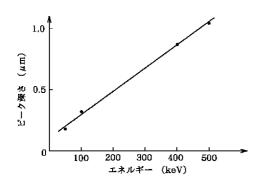

【0032】図7は、p型シリコン基板に対するボロンの注入エネルギーと、注入されたボロンの濃度が最大になる深さ(ピーク深さ)との関係をシミュレーションによって求めた結果を示している。図示するように、注入 エネルギーを変えることによってピーク深さをかなり広範に変化させることができ、所望の深さのところにチャネルストッパ領域となるp・層を形成することができる。

【0033】以下、具体例を挙げて、ボロンのドーズ量 や溝部(トレンチ溝)の深さの決定方法について説明す る。

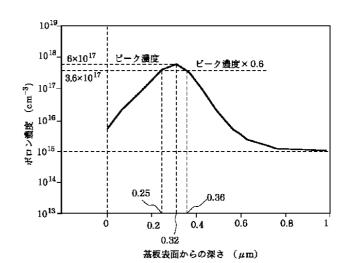

【0034】図8は、p型シリコン基板にボロンをドー ズ量 1 × 1 0<sup>13</sup> c m<sup>-2</sup>、注入エネルギー 1 0 0 k e V で イオン注入した場合のボロンの深さ方向分布(デプスプ ロファイル)をシミュレーションによって求めた結果を 示している。 p型シリコン基板 1 には、そもそも 1 x 1 0<sup>15</sup> c m<sup>-3</sup>の濃度でボロンが含まれているものとする。 この注入条件では、ピーク深さは 0.32 µ mとなり、 ピーク深さでのボロン濃度 (ピーク濃度)は $6 \times 10^{17}$ cm<sup>-3</sup>となる。そして、ピーク濃度の6割(3.6×1 0<sup>17</sup> c m<sup>-3</sup>)以上の濃度の領域は、深さが 0.25~0. 3 6 µ mの範囲となる。もし、深さ 0 . 2 5 µ mの位置 に3.6×10<sup>17</sup> c m<sup>-3</sup>の濃度でボロンが存在していて もサブスレッショルド特性に影響を及ぼさないとすれ ば、ドーズ量 1 x 1 0<sup>13</sup> c m<sup>-2</sup>、注入エネルギー 1 0 0 k e V でボロンをイオン注入するとともに、深さが 0. 3 2 μmとなるように溝部を開口すればよいことにな

【0035】もし、形成するMOSトランジスタが、基板表面から深さ0.25 $\mu$ mの位置に3.6 $\times$ 10<sup>17</sup>cm  $^{-3}$ の濃度でボロンが存在するとサブスレッショルド特性に影響が及ぼされるようなものである場合には、第2スレッショルド電圧 $V_{T2}$ を持つ程度にボロンのドーズ量を下げるか、あるいは、イオン注入時のエネルギーを高めてサブスレッショルド特性が劣化しない深さにボロンを注入し、かつ、それにあわせて溝部7も深く開口するすればよい。

【0036】以上、本発明の実施の一形態を説明したが、本発明は上述した形態のものに限定されるものではない。例えば、n型シリコン基板にpチャネルMOSトランジスタを形成する場合であれば、溝部の形成の前に、n型不純物として例えばヒ素(As)を基板にイオン注入して、n型シリコン基板の一定の深さのところに一様に、チャネルストッパ領域となるn・層を形成するようにすればよい。

50

[0037]

【発明の効果】以上説明したように本発明は、シリコン基板などの半導体基板の内部の一定の深さのところにイオン注入などによりチャネルストッパ領域となる層を予め形成し、その後、素子分離領域を構成する溝(トレンチ)を形成することにより、チャネルストッパ領域の形成時には溝が存在していないので、素子が微細化した場合であっても、サブスレッショルド特性を劣化させることなく素子分離特性を向上させることができるという効果がある。

## 【図面の簡単な説明】

【図1】本発明の実施の一形態の半導体装置の製造工程 を示す断面図である。

【図2】本発明の実施の一形態の半導体装置の製造工程を示す断面図であって、図1に示した工程に引き続く工程を示すものである。

【図3】本発明の実施の一形態の半導体装置の製造工程を示す断面図であって、図2に示した工程に引き続く工程を示すものである。

【図4】本発明の実施の一形態の半導体装置の製造工程 20 を示す断面図であって、図3に示した工程に引き続く工程を示すものである。

【図5】(a)はチャネルストッパのボロン濃度と素子間分離耐圧及びサブスレッショルド係数との関係を模式的に示すグラフであり、(b),(c)は空乏層とp-層との関係を模式的に示す断面図である。

【図6】(a)は基板表面からp·層までの距離dとサブスレッショルド係数Sと関係を示すグラフであり、(b)は距離dを説明する断面図であり、(c)は距離dが小さすぎるときの空乏層とp·層との関係を模式的に示す断面

図である。

【図7】ボロンの注入エネルギーとピーク深さとの関係 を示すグラフである。

【図8】イオン注入されたボロンの深さ方向分布の一例を示す図である。

【図9】(a)~(c)は、従来の半導体装置の製造工程を示す断面図である。

【図10】(a)~(c)は、従来の半導体装置の製造工程を示す断面図であって、図9に示す工程に引き続く構成を 10 示すものである。

## 【符号の説明】

1 p型シリコン基板

2,16,17 酸化膜

3 ボロンイオン

4 p · 層

5 絶縁膜

6,13,21 フォトレジスト層

8 室化膜

0 9,12 多結晶シリコン層

10 熱酸化膜

11 ゲート酸化膜

12a ゲート電極

14 リンイオン

15 n<sup>-</sup>層

16a サイドウォール

18 ヒ素イオン

19 n<sup>+</sup>層

20 層間絶縁膜

30 22 電極

【図7】

【図8】

層間絶縁膜

【図3】 【図4】 12 多結晶シリコン層 (a) (a) 21 フォトレジスト層 (b) (b) 12a 1,6 酸化膜 (c) 16a サイドウォール (c) (d) 【図9】 52 レジストパターン (a) 、 51 p型シリコン基板 53 溝部 (b) **`**51 53 <u>\_\_</u>52 (c) ·54 p¯領域

# 【図5】